Subscriber access provided by UNIV OF NEWCASTLE

## Functional Inorganic Materials and Devices

# High-performance all-printed amorphous oxide FETs and logics with electronically compatible electrode/ channel interface

Bhupendra Kumar Sharma, Anna Stoesser, Sandeep Kumar Mondal, Suresh K. Garlapati, Mohammed H. Fawey, Venkata Sai Kiran Chakravadhanula, Robert Kruk, Horst Hahn, and Subho Dasgupta

ACS Appl. Mater. Interfaces, Just Accepted Manuscript • DOI: 10.1021/acsami.8b04892 • Publication Date (Web): 12 Jun 2018

Downloaded from http://pubs.acs.org on June 12, 2018

## **Just Accepted**

"Just Accepted" manuscripts have been peer-reviewed and accepted for publication. They are posted online prior to technical editing, formatting for publication and author proofing. The American Chemical Society provides "Just Accepted" as a service to the research community to expedite the dissemination of scientific material as soon as possible after acceptance. "Just Accepted" manuscripts appear in full in PDF format accompanied by an HTML abstract. "Just Accepted" manuscripts have been fully peer reviewed, but should not be considered the official version of record. They are citable by the Digital Object Identifier (DOI®). "Just Accepted" is an optional service offered to authors. Therefore, the "Just Accepted" Web site may not include all articles that will be published in the journal. After a manuscript is technically edited and formatted, it will be removed from the "Just Accepted" Web site and published as an ASAP article. Note that technical editing may introduce minor changes to the manuscript text and/or graphics which could affect content, and all legal disclaimers and ethical guidelines that apply to the journal pertain. ACS cannot be held responsible for errors or consequences arising from the use of information contained in these "Just Accepted" manuscripts.

## High-performance all-printed amorphous oxide FETs and logics with electronically compatible electrode/ channel interface

Bhupendra K. Sharma, †,‡,\* Anna Stoesser, † Sandeep Kumar Mondal,§ Suresh Kumar Garlapati, † Mohammed H. Fawey, †,|| Venkata Sai Kiran Chakravadhanula, † Robert Kruk,† Horst Hahn,†,|| and Subho Dasgupta†,§

## **ABSTRACT**

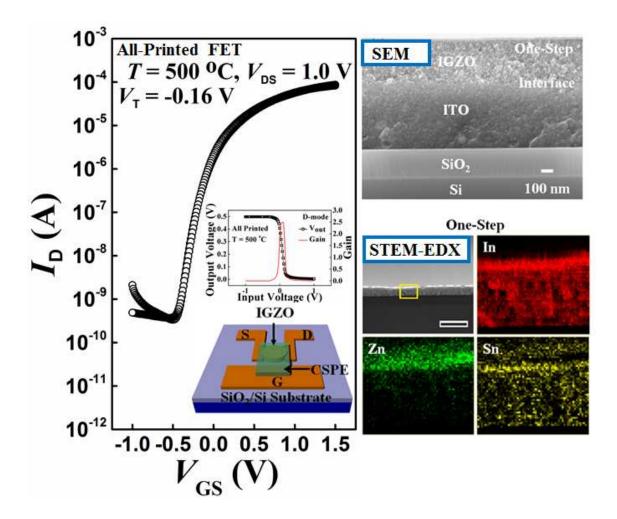

Oxide semiconductors typically show superior device performance compared to amorphous silicon or organic counterparts, especially, when they are physical vapor deposited. However, it is not easy to reproduce identical device characteristics when the oxide field-effect transistors (FETs) are solution-processed/ printed; the level of complexity further intensifies with the need to print the passive elements as well. Here, we developed a protocol for designing the most electronically compatible electrode/ channel interface based on the judicious material selection. Exploiting this newly developed fabrication schemes, we are now able to demonstrate high-performance all-printed FETs and logic circuits using amorphous indium-gallium-zinc oxide (a-IGZO) semiconductor, indium tin oxide (ITO) as electrodes and composite solid polymer electrolyte as the gate insulator. Interestingly, all-printed FETs demonstrate an optimal electrical performance in terms of threshold voltages and device mobility and may very well be compared with devices fabricated using sputtered ITO electrodes. This observation originates from the selection of electrode/ channel materials from the same transparent semiconductor oxide family, resulting in the formation of In-Sn-Zn-O

<sup>†</sup>Institute of Nanotechnology, Karlsruhe Institute of Technology (KIT), D-76344, Germany

<sup>&</sup>lt;sup>‡</sup>Centre for Nano Science and Engineering (CeNSE), Indian Institute of Science, Bangalore 560012, India

<sup>§</sup>Department of Materials Engineering, Indian Institute of Science, Bangalore 560012, India

Joint Research Laboratory Nanomaterials at Technische Universität Darmstadt (TUD), 64287, Germany

(ITZO) based diffused a-IGZO/ ITO interface that controls doping density while ensuring high electrical performance. Compressive spectroscopic studies reveal that Sn doping mediated excellent band alignment of IGZO with ITO electrodes is responsible for the excellent device performance observed. All-printed *n*-MOS based logic circuits have also been demonstrated towards new-generation portable electronics.

**Keywords:** ink-jet, all-printed, amorphous In-Ga-ZnO, electrolyte gating, FET and logic

## INTRODUCTION

Solution processing, easy fabrication, large area compatibility, cost effectiveness along with integration flexibility and stretchability are becoming the driving factors for the scientific community to carry out research in oxide-based next generation smart electronics. 1-4 In this context, the amorphous oxide semiconductors are becoming the most attractive choice as they possess an exceptional combination of properties that include high electronic performance, transparency, spatial homogeneity and somewhat superior mechanical properties than their crystalline oxide semiconductor counterparts.<sup>5–9</sup> However, their electronic performance is found to deteoriate once these materials are solution processed or printed as compared to when they are fabricated using physical vapor deposition (PVD) techniques. 10-12 Here, the motivation behind printing electronic circuitry is to enable a cost effective and easy fabrication route for large area and bulk volume of use-and-throw type consumer electronics. 13-19 However, it requires a wide range of scientific and technical knowledge in order to address various fundamental issues related to the printing processes, such as, the development of printing compatible materials, preparation of high quality inks, compliance of the prepared ink to the host substrate, when necessary additional surface treatment of the host substrates, process optimization for each printing components and so on.<sup>20</sup> However, it is to

be noted that the full potential of this technology may only be exploited when each and every component of a circuitry would be printed. Several attempts have been made in the recent times, where ink-jet printed semiconductor oxides have been used as the channel layer of fabricated FETs. 21-23 Among which few reports have even demonstrated complete room temperature fabrication of printed devices showing its potential in additive manufacturing techniques on inexpensive and flexible substrates.<sup>22</sup> However, in most of the previous attempts, only the channel layer has been printed, whereas the rest of device components have been fabricated using various high-cost alternatives (e.g. different PVD techniques). 24-28 Therefore, it can be stated that in this ongoing quest of printed logic electronics, the primary focus has always been concentrated around optimizing the superior quality of active materials. The passive components of the FETs are often forgotten. Interestingly, the scenario may completely change if each and every component of a device is printed. Understandably, it is indeed difficult to print the passive structures with narrow channel lengths, and in addition, due to the spatial inhomogeneity and high roughness resulting from the printed coarse-grained inorganic semiconductor layer, the channel length sensitivity may become a matter of concern for the all-prinetd long-channel thin film transistors (TFTs). Recently, as a rare example of all-printed TFTs, Scheideler et al. have demonstrated low temperature (≤ 250 °C) fabrication of FETs by printing an aqueous ink based aluminum doped cadmium oxide as source/ drain (S-D) electrodes and indium oxide as the channel element.<sup>23</sup>

In this context, here we show that high-performance all-printed devices can be realized using a-IGZO as the channel layer, in combination with precursor derived printed transparent conducting oxide electrodes, such as ITO with an excellent band alignment at the S-D/channel interface, resulting in near Ohmic contacts. It is again non-trivial to obtain an easy-to-print high-performance dielectric. In the present study, a composite solid polymer electrolyte (CSPE) as an electronic insulator has been used, which is at the same time easy-to-print, non-toxic and can show adequate thermal and environmental compatibility. <sup>21,29,30</sup> On the other

hand, the very high capacitance  $(1-10~\mu\text{F/cm}^2)$  of the electrolytes significantly reduces the operation voltage requirement down to 1-2 volts and makes the devices completely battery compatible and suitable for portable electronic applications.

In case of all-printed devices, the selection of material is quite crucial; mimicking the approach of modern Si-technology, where heavily doped silicon is used as the drive electrodes, here we have chosen ITO, which is a heavily doped transparent conducting oxide (TCO), as the electrode material. Such a selection from the similar material family with maximum possible common constituents may right-away provide an opportunity to have a superior electronically compatible interface (especially, when all the device components are solution processed/printed), by self-organizing or re-structuring atoms at the interface region. Furthermore, in order to facilitate mixing of atoms of individual layers at the interface, same solvents have been used during the preparation of the precursor inks. It may be noted that the selection of ITO as the passive electrodes is certainly not new, however, here we would like to take full advantage of ITO as the electrode material by forming a electronically compatible diffused interface layer upon annealing. Although usually not practiced, the effect of the intentional intermixing of atoms at the metal/ semiconductor interface is found to be beneficial in the present study to control carrier density at the channel layer ensuring channel conductance at zero gate, at the same time, ensuring high device performance, in terms of field-effect mobility. Finally, we also demonstrate and compare all-printed n-MOS based inverters with various load conditions.

## **EXPERIMENTAL SECTION**

**Ink Preparation.** IGZO: A 0.1 M parent solutions of In(NO<sub>3</sub>)<sub>3</sub>•xH<sub>2</sub>O, Ga(NO<sub>3</sub>)<sub>3</sub>•xH<sub>2</sub>O and Zn(CH<sub>3</sub>COO)<sub>2</sub>•2H<sub>2</sub>O are prepared separately using the mixture of 2-methoxyethanol and ethylene glycol organic solvents with a volume ratio of 8:2, respectively.

The appropriate volumes of these parent solutions are mixed in an atomic ratio of In: Ga: Zn = 63:7:30 and continuously stirred for one hour to prepare a clear transparent precursor ink for IGZO. ITO: Indium nitrate hydrate (99.9 %,) and tin(IV) chloride pentahydrate (99.9 %,) are separately dissolved in 2-methoxyethanol. These solutions are mixed in the cation ratio of In: Sn = 9:1 and stirred for one hour to prepare a clear transparent precursor ink for ITO. Composite Solid Polymer Electrolyte (CSPE): The electrolyte is obtained by stirring the clear solution of 0.3 g PVA in 6 g of DMSO together with a solution of 0.07 g LiClO<sub>4</sub> in 0.63 g PC. The stirring is carried out overnight (~12 hours) in order to properly homogenize the electrolyte ink.

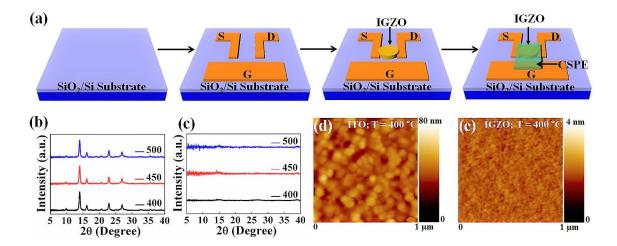

**Device Fabrication.** All devices are fabricated on cleaned SiO<sub>2</sub>/Si substrate. SiO<sub>2</sub>/Si substrate is cleaned using standard piranha treatment (i.e. submersing in 3:1 volume ratio of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> for 10 minutes). After cleaning, substrates are washed thoroughly with a copious amount of DI water and dried just before the use. The all-printed FETs are fabricated with the printing of ITO ink as two parallel lines (S-D electrodes) and an equidistant rectangle (G electrode in the displaced/in-plane geometry) as shown schematically in the Figure 1a. Subsequently, the ITO-based printed coplanar passive structure is dried at 130 °C for 30 minutes on a hot plate in ambient air. Next, the semiconducting IGZO layer has been printed to bridge the S-D electrodes and subsequently dried at 130 °C for 30 minutes. At this stage, the printed devices are annealed at 400, 450 and 500 °C for 1 hour through one-step heating. In order to comprehend the effect of one-step heating, the devices are also prepared with two separate steps annealing, one annealing step for printed ITO (at 500 °C) and the other for printed a-IGZO (at 400 °C). The devices with lithographically patterned sputtered ITO electrodes and printed a-IGZO (annealed at 400 °C and 500 °C) have also been fabricated for comparison purpose. At the last step, the fabrication of FET is completed with the printing of CSPE gate insulator layer that cover the a-IGZO channel completely and the ITO gate

electrode partially (see Figure 1a for complete fabrication steps). The channel length and width of the devices with sputtered ITO passives were stricktly maintened at 50 and 100  $\mu$ m, respectively; for the all-printed FETs, owing to limited accuracy of the printing process itself, the device dimensions may have varied by  $\pm$  10  $\mu$ m, however, high resolution optical images were used in each case to ascertain the channel dimentions, which would later be used for the mobility calculations. For the capacitance measurement, two in-plane parallel electrodes test structures were fabricated and CSPE was printed to cover both the terminals. One terminal was composed of lithographically patterened sputtered ITO, while the other was printed and annealed a-IGZO.

## RESULTS AND DISCUSSIONS

Figure 1a shows the complete fabrication steps of the all-printed FETs in a sequential manner. Source (S), drain (D) and gate (G) electrodes were printed on a cleaned SiO<sub>2</sub>/ Si substrate using ITO precursor based ink. After the ITO ink is dried, the IGZO precursor ink was printed to form the semiconductor channel layer and subsequently dried. These printed structures are then annealed through either one-step or two-steps annealing processes and finally the CSPE layer is printed to cover the channel region completely and the gate electrode partially. The thickness of printed ITO and IGZO has been measured by profilometer and estimated to be 150 nm and 70 nm, respectively. Prior to the electrical measurements, systematic structural and morphological characterizations of the annealed ITO and IGZO layers have been carried out at different temperatures. The XRD patterns of ITO and IGZO layers, spin-coated onto SiO<sub>2</sub>/ Si substrates and subsequently annealed at ~400, 450 and 500 °C temperatures are shown in Figures 1b and 1c, respectively. The annealing transforms the ITO precursor into a polycrystalline phase, whereas the IGZO remains amorphous in nature. The XRD patterns of annealed ITO layers exhibit characteristic peaks at 13.97°,

16.14°, 22.93° and 26.93°, which correspond to (222), (400), (431) and (440) reflections of cubic structure of In<sub>2</sub>O<sub>3</sub>, respectively. The crystallite size of ITO annealed at 400, 450 and 500 °C has been calculated using Debye-Scherrer equation from the full-width at halfmaximum of (222) peak and found to be 15.9, 16.3 and 17.1 nm, respectively. The atomic force microscopy (AFM) images of ITO and a-IGZO were recorded on real FET device annealed at 400 °C which is shown in Figures 1d and 1e, respectively. The root mean square value of roughness  $(R_{\rm rms})$  for ITO was found to be 5.8 nm, however, in comparison, the  $R_{\rm rms}$ value for a-IGZO was estimated to be much smaller, 0.25 nm only, which is typically the case for predominantly amorphous films; in absence of granular crystalline phases, the surface appears extremely smooth and homogeneous. In the present study, the solution processed ITO ink has been printed as electrodes in fabricating the FETs, hence, it is believed to be important to compare the sheet resistance of solution processable ITO with the commercially available sputtered ITO of comparable thickness (both around 150 nm). The sheet resistance has been measured using van der Pauw geometry in both cases and its variation for spin-coated ITO precursor ink with respect to annealing temperatures is shown in Figure S1. The sheet resistance of solution processed ITO films is found to be  $1.5 \times 10^4$   $\Omega/\Box$  at 400 °C and it decreased down to  $2.5 \times 10^3~\Omega/\Box$  at 500 °C annealing temperature. The decrease in measured sheet resistance may primarily be related to a relatively superior densification and low porosity/ structural defects in the higher temperature annealed films. These sheet resistance values compare reasonably with the earlier reports, however, it is substantially higher as compared to the commercially available sputtered ITO which typically shows a sheet resistance value of only 15  $\Omega/\Box$ , about two orders of magnitude lower than the solutionprocessed films. Here, the high sheet resistance value of the solution processed ITO can be attributed to the large degree of structural defects, micro-cracks, porosity and low density of grains as compared to the physical vapor deposited films. While, a substantial decrease in resistance may be possible when the solution derived films are annealed in special reducing

atmosphere, <sup>31,32</sup> such practices are not suitable for device fabrication, especially, when performing one-step annealing along with the semiconductor layer.

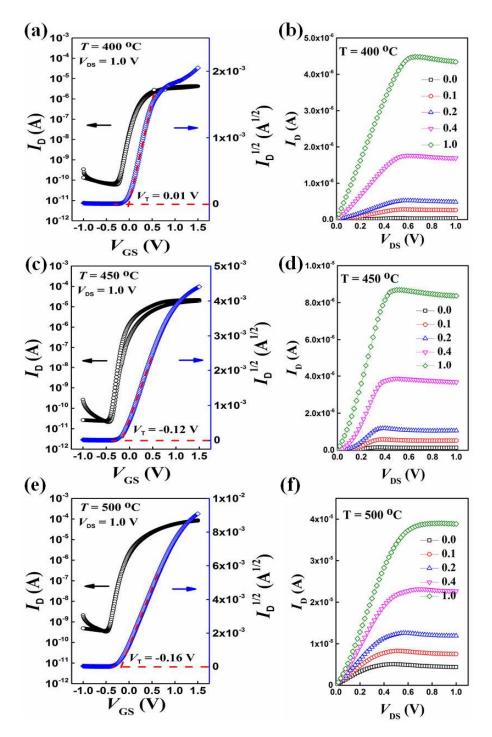

The transfer and output characteristics of the all-printed FETs for one-step annealing at different temperatures are shown in Figure 2. The transfer curves are presented in Figure 2a, c, and e for 400, 450 and 500 °C annealing temperatures, respectively, for a constant drain to source voltage  $(V_{\rm DS})$  of 1.0 V. The FETs show good device performance within the low operating voltage range (± 1.0 V) due to the high capacitance of the CSPE insulator. The output characteristics are presented at different V<sub>GS</sub> in Figure 2b, d and f for 400, 450 and 500 °C annealed devices, respectively. The output characteristics show a linear behavior at low  $V_{\rm DS}$  region, thereby ensuring near Ohmic S-D (ITO)/ channel (a-IGZO) interface. While, the saturation behavior for higher  $V_{\rm DS}$  indicates a complete pinch-off of the channel, occasionally a slight decrease in the saturation current has been observed, which can be attributed to the negative differential resistance (NDR) effect.<sup>33</sup> It can be noticed that all the devices including the 400 °C annealed ones have shown good switching behavior. However, at 400 °C annealing, the resistance of ITO is found to be four orders higher than the sputtered ITO (Figure S1), as a result, at this temperature the on current  $(I_{on})$  seems to be limited largely by the printed ITO passives. This is apparent with sudden saturation of drain current  $(I_{D.sat})$ after 0.5 V  $V_{GS}$  (Figure 2a). Hence, a large increase in  $I_{D,sat}$  has been recorded for devices annealed at higher temperatures (Figure 2c and e). Furthermore, the on/off current ratio ( $I_{on/off}$ ) has also been found to increase for 450 and 500 °C annealed devices as compared to the 400 °C annealed ones, (Table 1), whereas the threshold voltage (V<sub>T</sub>) and subthreshold swing (SS) values are calculated to be almost identical, around  $0 \pm 0.1$  V and  $100 \pm 10$  mV decade<sup>-1</sup>, respectively. It is to be noted that these extracted FET parameters can be compared well to the FETs fabricated using PVD-grown electrodes with printed semiconductor (a-IGZO) layer. 24,26 Here, it is interesting to note that even though the printed ITO electrodes possess considerably

higher sheet resistance values (Figure S1) as compared to the sputtered ones, the all-printed FETs demonstrate attractive transistor characteristics that further improves with temperature.

Generally, the nitrate and acetate based metal precussors that are used to obtain IGZO precursor decomposes below 300 °C and complete removal of any remaining organic residues takes place within the temperature range of 300-400 °C. Therefore, this is the typically chosen temperature range for solution processed IGZO;<sup>26,33–38</sup> a further increase in annealing temperature increases the initial doping (free carrier) concentration, leaving the material conducting and resulting in depletion mode MOSFET behavior.<sup>39,40</sup> On the other hand, the carrier concentration at a particular annealing temperature also depends strongly on the relative ratio of In: Ga: Zn.<sup>40</sup> In general, solution processed IGZO is preferably annealed at 350 – 400 °C for FET fabrication.<sup>39</sup> Therefore, when investigating the effect of two stage annealing, the IGZO layer has been annealed at 400 °C.

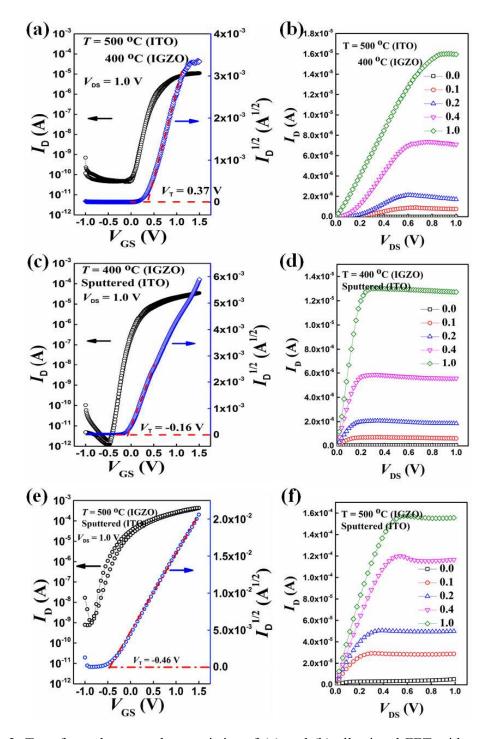

The transfer and output characteristics for such two-steps annealed FETs are shown in Figures 3a and 3b, respectively. FET parameters for two-steps annealed device are extracted and compared with one-step annealed FET characteristics (Table 1). For the two-steps annealing process, the  $I_{on/off}$ ,  $V_T$  and SS values are estimated to be as  $\sim 10^5$ , 0.37 V and 110 mV decade<sup>-1</sup>, respectively. Next, in order to compare our all-printed device results with the standard practice, identical TFTs have also been prepared with sputtered ITO passives (Figure 3c-3f). In this case, the printed IGZO layer was annealed at both 400 °C and 500 °C, respectively. In accordance with previous reports, a high carrier doping, resulting in a strong negative shift of threshold voltage (around -0.5 V) has been observed when the annealing temperature was raised to 500 °C.

In addition to  $I_{on/off}$ ,  $V_T$ , and SS, the other most important parameter by which FET performance can be evaluated is device mobility ( $\mu_{FET}$ ). The  $\mu_{FET}$  is considered to be the most important one to assess the quality of the semiconductor material and the semiconductor/

insulator interface. The  $\mu_{\text{FET}}$  values of all the devices are calculated using the following equation;

$$\mu_{FET} = 2LI_{ds} / [WC_{dl}(V_{qs} - V_{th})^2] \tag{1}$$

where, L and W are the length and width of the channel;  $I_{\rm DS}$  and  $C_{\rm dl}$  are the drain current and the double layer capacitance of the electrolytic insulator at desired  $V_{\rm GS}$  values (the value of gate voltage where the device mobility,  $\mu_{\rm FET}$ , is calculated), respectively. Here, all the parameters can be estimated using the FET's physical dimensions and electrical characteristics except  $C_{\rm dl}$ . On the other hand, in case of electrolyte as gate insulator approach, the double layer capacitance value changes dramatically with continuous charge accumulation with the  $V_{\rm GS}$  sweep. Therefore, a careful estimation of  $C_{\rm dl}$  with respect to varying  $V_{\rm GS}$  values is absolutely essential to estimate the device mobility accurately.

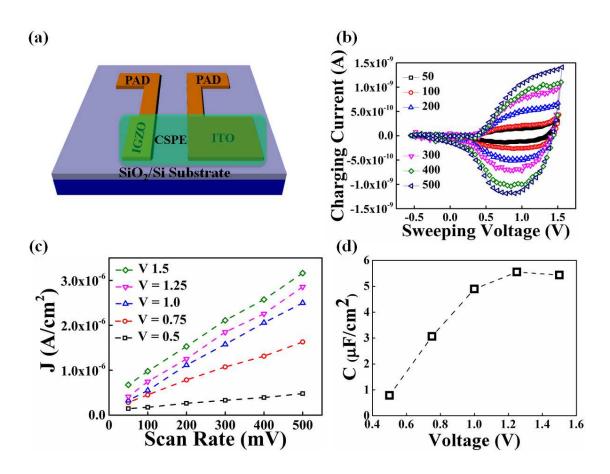

Although an electrolyte is used as the gate insulator, qualitatively the behavior of the metal-insulator-semiconductor capacitor (MISCAP) (composed of the gate electrode (ITO)/ electrolyte/ semiconducting a-IGZO) utilized in the present study compares well with the space charge density plots of metal-oxide-semiconductor field-effect transistors (MOSFETs). In the present study, the double layer capacitance ( $C_{\rm dl}$ ) of the a-IGZO/ electrolyte interface is calculated using cyclic voltammetry measurements on coplanar structures that are identical to the in-plane FET device geometry (Figure 4a). Figure 4b shows the cyclic voltammograms indicating the behavior of charging current as a function of the sweeping voltage at different scan rates. Current loops are observed to be closed but non-symmetric as can be expected for charge accumulation and depletion at the semiconductor interface. The sign of sweeping voltage is analogous to the gate voltage, and hence at positive sweeping voltage electrons accumulate at the a-IGZO surface and charging current increases. Electron depletion takes place in the opposite direction of sweep, a-IGZO being an n-type semiconductor, this results in a decrease in total surface charge density and a decrease in charging current. The current density (J) values are calculated using the overlapped area between CSPE and an a-IGZO

electrode for 0.5, 0.75, 1.0, 1.25 and 1.5 V applied sweeping voltages, which is plotted against different scan rates, as shown in Figure 4c. Interestingly, the current density versus scan speed plots are quite linear which can be taken as a proof of predominant capacitive coupling at the a-IGZO/ electrolyte interface; any slight deviation from the ideal scaling situation (current density should be proportional to dV/dt) can be due to little overlap of the electrolytic insulator with ITO contact pads (parasitic charging). The capacitance values at every applied potential can now be calculated using the slope of the current density versus scan rate plots and are found to be 0.78, 3.06, 4.89, 5.55 and 5.43  $\mu$ F/cm<sup>2</sup> for 0.5, 0.75, 1.0, 1.25 and 1.5 applied sweeping voltages, respectively. These values are plotted as a function of different applied voltages showing a linear increase up to 1.0 V and then a somewhat saturation (Figure 4d), again typical behavior for a MISCAP device. Therefore, the identical co-planar structure used for the capacitance calculation provides an extremely realistic estimation of the double layer capacitance at every  $V_{GS}$  values and thus enable device mobility calculation at various gate voltages.

The variation of FET parameters ( $V_T$ ,  $I_{\text{on/off}}$ , SS and  $\mu_{\text{FET}}$ ) for all-printed one-step, two-step annealed and sputtered ITO/ printed a-IGZO devices are summarized and compared in Table 1. From Table 1, it is evident that parameters like  $I_{\text{on/off}}$  is identical for every alternate treatment that has been performed and adequate for logic operations; the value of SS hovers around 100 mV/dec, which ensures low voltage switching, and again found to be fairly independent of the various fabrication routines that we have excercized. However, there have been large spread in the important performance parameter, field-effect mobility; the mobility values are found to be less than 10 cm<sup>2</sup>/Vs, for any device, where the printed IGZO has been annealed at 400 °C (in accordance with most of the publications involving solution processed IGZO, Table S1), higher performance has been recorded only for FETs annealed at 500 °C. While, typically the amorphous oxides are not recommended to be annealed above 400 °C, which results in very high carrier concentration and high negative threshold voltages. Here,

we find that our representive all-printed one-step annealed IGZO devices show a high mobility value (15.5 cm<sup>2</sup>/Vs) without showing considerably high channel conductance at zero gate. This observation would later be explained based on the interfacial intermixing of components at the electrode/ channel interface. In contrast, the FETs prepared from sputtered ITO passives and annealed at 500 °C show slightly higher mobility value than the one-step annealed diffused ITO/ a-IGZO interface devices, however, at the cost of high zero gate channel currents and a highly negative threshold voltage value. The high performance of our all-printed devices, which is easily among the best reported values for solution processed/ printed IGZO TFTs<sup>33–36</sup> is highly interesting given the fact that the printed ITO electrodes show orders of magnitude inferior conductivity as compared to the sputtered ITO passives. The comparable device mobility (with respect to standard sputtered passive FETs) coupled with near accumulation-mode device performance of our one step annealed all-printed FETs indicates that the physical, chemical and electronic compatibility of the semiconductor/ electrode interface must be playing an important role in deciding the device performance. Therefore, the investigation of the interface between S-D ITO electrodes and the a-IGZO channel is sought after.

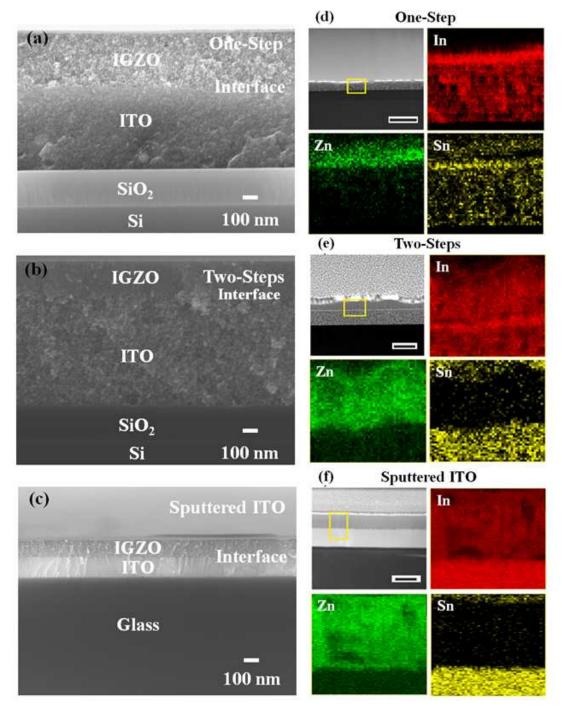

Cross-sectional scanning electron microscopy (SEM) images of interface of one-step annealed (at 400 °C), two-step annealed (first at 500 °C and then at 400 °C for IGZO) and sputtered ITO/ printed a-IGZO (annealed at 400 °C) are shown in Figure 5a, b, and c, respectively. It is evident that in all-printed one-step and two-step annealed samples, a diffused interface between the a-IGZO and ITO passives can be noticed whereas a relatively sharp interface boundary is observed for the sputtered ITO/ printed a-IGZO sample. The diffusion at the interface in all-printed devices can be attributed to the physical compatibility resulting in superior intermixing in the respective oxide layers, as both the materials are solution processed. Here, one may correlate the electrical performance of the all-printed FETs with the diffusive nature of the a-IGZO/ ITO interface. Such diffused region often hampers

electronic transport; however, in this case, ITO and a-IGZO belong to the identical transparent oxide family; thus, intermixing at the interface may result in the restructuring/reorganization among constituent elements leading to the electronically compatible region which may not actually reduce the semiconductor mobility, however, control the initial doping density. especially for high temperature annealed devices. In order to obtain a better resolution and complete insight of the elemental distribution in the diffused interface region, identical crosssectional analysis is performed on all the samples using high-resolution transmission electron microscopy (HRTEM). The TEM results are found to corroborate the SEM observations; the all-printed devices show the diffused a-IGZO/ITO interface, marked by dashed rectangle (Figures S2a and S2b), however, the width of the diffused interface is found to be significantly smaller for all-printed two-step annealed sample, as compared to one-step annealed one. This is obvious as in the case of two-step heating, the intermixing and diffusion at the interface must be limited by the already crystalline ITO (through the first step of annealing). In contrast to these two instances, a sharp interface boundary in sputtered ITO/ printed a-IGZO (Figure S2c) indicates that there is no or very little interdiffusion taking place across the sputtered ITO interface. In addition, the formation of lattice fringes at ITO regions implies its crystalline nature in all three cases (Figure S2a, b, and c). At the next step, in order to investigate the distribution of the constituent elements, scanning transmission electron microscopy electron dispersive X-ray (STEM-EDX) mapping has been performed across the interface as shown Figure 5 (d-f). It is evident from the elemental maps that the constituents are present as per expectation, in the respective layers (In, Sn in ITO; In, Zn in a-IGZO), however, the distribution of Sn (Figure 5d, e and f, bottom panel, right) is found to be largely dependent on the fact whether both ITO and a-IGZO layers are printed and the necessary annealing process is carried out in one-step or in two-steps. Identical inter-diffusion behavior has also been observed by Kim et al. for the spin coated GaO and InZnO layers which at the end resulted in a complete intermixing and formation of IGZO semiconducting laver. 41 Here.

for the all-printed one-step annealed sample, the distribution of Sn is found to be in ITO, as well as within the a-IGZO layer across the interface (Figure 5d, bottom panel, right). This observation indicates that Sn from  $In_{(1-x)}$ -Sn<sub>x</sub>-O (ITO layer) can easily diffuse into the amorphous In-Ga-Zn-O matrix (a-IGZO layer) while the other elements primarily remain in their respective layers. In comparison, the interlayer Sn diffusion is found to be insignificant for all-printed two-step annealed sample (Figure 5e, bottom panel, right), whereas, for the sputtered ITO and printed a-IGZO sample, Sn does not diffuse into the a-IGZO layer at all (Figure 5f, bottom panel, right).

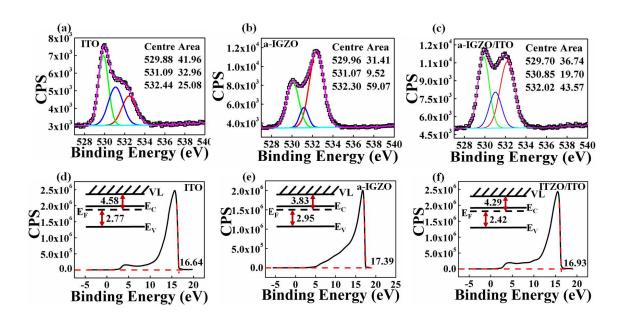

Here, it is important to note that the diffusion of Sn from ITO to a-IGZO in all-printed devices may lead to a change in the electronic environment across the interface; therefore, it is necessary to investigate the electronic structure of a-IGZO/ ITO interface. Consequently, qualitative as well as quantitative studies are performed using the photoelectron spectroscopy measurements on the one-step annealed a-IGZO/ ITO sample. The core level spectra of constituents (In, Sn, Ga, and Zn) for ITO, a-IGZO, and a-IGZO/ ITO is shown in Figure S3 which do not show a significant shift from one sample to another except slight shift of In and Ga peaks towards lower binding energy for a-IGZO/ ITO sample. Oxygen spectral peak (O 1S) which usually deconvolutes into three nearly Gaussian peaks, contains the information of its contributions to bond with metallic ions (529.5 eV), vacancies (530.5 eV) and adsorbed species such as -CO<sub>3</sub>, -OH etc. (532.5 eV). 42,43 The deconvoluted peaks, their corresponding centers and areas (%) for ITO, a-IGZO and a-IGZO/ITO interfacial region is shown in Figure 6a, b, and c, respectively. Here, it is evident that a-IGZO top surface is more favorable for external loosely adsorbed oxygen species as compared to ITO. It is probably due to the presence of Zn in a-IGZO which has more affinity to oxygen.<sup>44</sup> The a-IGZO/ ITO interface shows the intermediate result of a-IGZO and ITO alone for these adsorbed species. In addition to core levels spectra, depth profiling and ultraviolet photoelectron spectroscopy (UPS) studies have been carried out to obtain a closer look at the interface and the band structure

information. The depth profiling of a-IGZO/ ITO indicates that initially In, Ga and Zn core levels appeared, however, with further depth profiling (towards the interface), Sn feature also starts to appear along with In, Ga, and Zn (see Table S2). The content of In and Zn does not change significantly at further deep inside the interface, however, relatively small but a noticeable decrease in Ga and an increase in Sn can be observed. Here, we are expecting that low ionic radius of Sn makes it suitable to sit onto the Ga sites in the amorphous In-Ga-Zn-O matrix by replacing the Ga atoms. Furthermore, the shift of Ga binding energy towards lower side (breaking the oxidation of Ga) with depth profiling of the a-IGZO/ ITO interfacial region corroborates this argument. The substitution of Sn at Ga site leads to the formation of In-Sn-Zn-O (ITZO) locally which provides the extra electron and, thus, the formation of more conducting ITZO at the interface. Figure 6d, e, and f show the UPS spectra for ITO, a-IGZO and at a-IGZO/ ITO interface region where Sn starts to appear after depth profiling. The position of the valence band maxima is estimated using tangent at the onset of photoemission (see Figure S4) with respect to the Fermi level (E<sub>F</sub>) and the values of work function are estimated as a difference between incident energy (He-I, 21.22 eV) and the secondary cutoff. These estimated values are shown in the proposed schematic band diagram, (Inset of Figure 6 (d-f)). At a-IGZO/ ITO interface, the difference between the work functions (0.75 eV) of both materials may lead to high barrier height with the subject to the alignment of E<sub>F</sub>. While in case of ITZO/ ITO interface, the difference reduces down to 0.29 eV, and thus, the barrier height decreases significantly (Figure S5). In other words, this intermediate layer of ITZO, between the ITO electrode and the a-IGZO semiconductor layer offers excellent band alignment all the way across the interface; the interlayer work function difference is never too high, i.e. a large band bending is never required. On one hand, this ensures easy carrier transport across the intermediate layer, which enables near Ohmic contact and high carrier mobility, on the other hand, the diffused layer controls the the carrier concentration and channel conductance.

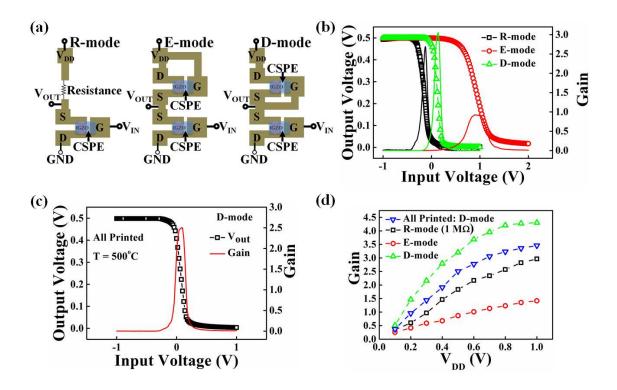

At the next level, the all-printed FETs are integrated together to fabricate simple logic units; various n-MOS based unipolar inverters with different types of loads, such as, a resistor (R-mode), an enhancement type n-MOS (E-mode) and a depletion type n-MOS (D-mode), as shown schematically in Figure 7a. Initially, the inverter circuits are constructed with sputtered ITO electrodes in order to figure out the most suitable load and then it is reproduced with the all-printed FETs. For all these fabricated inverter circuits, the channel (50 µm, for both drive and load FETs) and the number of printing pass for a-IGZO (2 layers, leading to 70 nm thickness) are kept constant. Figure 7b shows the input-output characteristics of fabricated inverters along with their signal gain profiles for sputtered ITO and printed a-IGZO in Rmode, E-mode and D-mode configurations, respectively with a drive voltage of  $V_{DD} = 0.5 \text{ V}$ . Typically, inverter performance is characterized by its signal gain value (gain=  $dV_{\text{out}}/dV_{\text{in}}$ ). However, in the case of unipolar inverters, the signal gain is not only determined by the performance of the drive FET but also by the load characteristics (see Figure S6). Here, the inverters fabricated with sputtered ITO and printed a-IGZO show the signal gain values of 2.6, 0.9 and 3.0 for R-mode (1 M $\Omega$ ), E-mode and D-mode devices, respectively, at  $V_{\rm DD} = 0.5$  V, indicating that D-mode load is most suitable. At the next step, the all-printed inverter circuit is fabricated by employing one-step heating process at 500 °C with the D-mode load. The inputoutput characteristic is shown in Figure 7c; here a signal gain of 2.5 is obtained for  $V_{\rm DD} = 0.5$ V. The signal gain value in present work is not significant but comparatively superior to earlier reported solution process oxide of similar configuration. 45-47 Figure 7d shows a comparison of signal gain values for sputtered ITO and all-printed inverters for varying input signal values. It is believed that a more careful optimization of the selected load profile with respect to the device characteristic of the drive FETs can certainly improve the performance of these all-printed inverters.

## CONCLUSIONS

Oxides based electrolyte-gated, all-printed FETs and logic inverters are successfully demonstrated here in this study, which show performances comparable to the devices that are fabricated using lithographically patterned and sputtered ITO electrodes. The excellent device characteristics of the all-printed FETs, even with an inferior electrode quality, can be attributed to the formation of diffused a-IGZO/ ITO interfaces, which allows annealing at higher temperatures without rendering the zero gate channel conductance too high. The crosssectional microscopic studies clearly identify the diffused regions at the interface, where Sn from ITO layer is found to get substituted at the Ga site in IGZO phase and the XPS investigations reveal that the reorganization of constituent elements at the atomic level leads to a diffused variation of Fermi level at the interface. In other words, an excellent band alignment from the electrode to the intermediate Sn-rich IGZO layer (or a-ITZO) and the said a-ITZO layer to the semiconducting a-IGZO layer exist, which, in turn, results in excellent near Ohmic contacts, high carrier mobility and controlled channel conductance upon annealing at higher temperatures. Undoubtedly, the selection of the electrode and semiconductor materials, stemming from identical material family, has facilitated the diffused interface formation and excellent band alignment. It may be concluded here that the present findings and the scientific understanding acquired in this study, which are also well supported by the comprehensive microscopic and spectroscopic measurements we have performed, may actuallygo beyond the scope of printed electronics.

#### ASSOCIATED CONTENT

## **Supporting Information**

The Supporting Information is available free of charge on the ACS Publications website at DOI:

Experimental details, Table S1 for comparing our results with earlier reported work, Table S2, Sheet resistance data, HR-TEM cross-sectional images, XPS data, Scheme of band diagram, Scheme of output and load ckaracterstics for inverter, References.

## ■ AUTHOR INFORMATION

## **Corrosponding Author**

\*Email: bksharmag@gmail.com (or bhupendras@iisc.ac.in)

Address: Centre for Nano Science and Engineering (CeNSE), Indian Institute of Science, Bangalore 560012, India

## **ORCID**

Bhupendra Kumar Sharma: 0000-0002-0247-5312

## **Notes**

The authors declare no competing financial interest.

## **ACKNOWLEDGEMENTS**

Bhupendra K. Sharma greatly acknowledges the visiting scientist fellowship provided by Institute of Nanotechnology, Karlsruhe Institute of Technology, Germany and Department of Science and Technology (DST), Ministry of Science and Technology, India for the award of DST-INSPIRE faculty program (No.: DST/INSPIRE Faculty Award/2014/MS-15; Code: IFA14-MS-15). HH and SD would like to acknowledge the financial support by Helmholtz Gemeinschaft in the form of Helmholtz Virtual Institute VI-530. Centre for Nano Science and

Engineering (CeNSE), Indian Institute of Science Bangalore is greatly acknowledged for providing the XPS, UPS and few electrical measurements facilities.

#### REFERENCES

- (1) Kim, Y.-H.; Heo, J.; Kim, T.-H.; Park, S.; Yoon, M.; Kim, J.; Oh, M. S.; Yi, G.; Noh, Y.; Park, S. K. Flexible Metal-Oxide Devices Made by Room-Temperature

Photochemical Activation of Sol–gel Films. *Nature* **2012**, *489* (7414), 128–132.

- (2) Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-Temperature Fabrication of Transparent Flexible Thin-Film Transistors Using Amorphous Oxide Semiconductors. *Nature* **2004**, *432* (7016), 488–492.

- (3) Banger, K. K.; Yamashita, Y.; Mori, K.; Peterson, R. L.; Leedham, T.; Rickard, J.; Sirringhaus, H. Low-Temperature, High-Performance Solution-Processed Metal Oxide Thin-Film Transistors Formed by a 'Sol–gel on Chip' Process. *Nat. Mater.* 2011, 10 (1), 45–50.

- (4) Heremans, P.; Tripathi, A. K.; Meux, A. D. J. De; Smits, E. C. P.; Hou, B.; Pourtois, G.; Gelinck, G. H. Mechanical and Electronic Properties of Thin-Film Transistors on Plastic, and Their Integration in Flexible Electronic Applications. 2016, 4266–4282.

- (5) Chen, H.; Cao, Y.; Zhang, J.; Zhou, C. Large-Scale Complementary Macroelectronics Using Hybrid Integration of Carbon Nanotubes and IGZO Thin-Film Transistors. *Nat. Commun.* 2014, 5, 4097 (1-12).

- (6) Sharma, B. K.; Jang, B.; Lee, J. E.; Bae, S.-H.; Kim, T. W.; Lee, H.-J.; Kim, J.-H.; Ahn, J.-H. Load-Controlled Roll Transfer of Oxide Transistors for Stretchable Electronics.

Adv. Funct. Mater. 2013, 23 (16), 2024-2032.

- (7) Fortunato, E.; Barquinha, P.; Martins, R. Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances. *Adv. Mater.* **2012**, *24* (22), 2945–2986.

- (8) Jariwala, D.; Sangwan, V. K.; Seo, J. T.; Xu, W.; Smith, J.; Kim, C. H.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Large-Area, Low-Voltage, Antiambipolar Heterojunctions from Solution-Processed Semiconductors. 2015, 15, 416-421.

- (9) Luo, H.; Wellenius, P.; Lunardi, L.; Muth, J. F. Transparent IGZO-Based Logic Gates. **2012**, *33* (5), 673–675.

- (10) Ahn, B. Du; Jeon, H.; Sheng, J.; Park, J.; Park, J.-S. A Review on the Recent Developments of Solution Processes for Oxide Thin Film Transistors. *Semicond. Sci. Technol.* 2015, 30 (6), 064001 (1-15).

- (11) Jeong, S.; Ha, Y.; Moon, J.; Facchetti, A.; Marks, T. J. Role of Gallium Doping in Dramatically Lowering Amorphous-Oxide Processing Temperatures for Solution-Derived Indium Zinc Oxide Thin-Film Transistors. *Adv. Mater.* 2010, 22 (12), 1346– 1350.

- (12) Yu, X.; Marks, T. J.; Facchetti, A. Metal Oxides for Optoelectronic Applications. *Nat. Publ. Gr.* **2016**, *15* (4), 383–396.

- (13) Liu, X.; Tarn, T.; Huang, F.; Fan, J. Particuology Recent Advances in Inkjet Printing Synthesis of Functional Metal Oxides. *Particuology* **2015**, *19*, 1–13.

- (14) Calvert, P. Inkjet Printing for Materials and Devices. **2001**, 3299–3305.

- (15) Choi, C.; Lin, L.-Y.; Cheng, C.-C.; Chang, C. Printed Oxide Thin Film Transistors: A Mini Review. *ECS J. Solid State Sci. Technol.* **2015**, *4* (4), P3044–P3051.

- (16) Wu, W. Inorganic Nanomaterials for Printed Electronics: A Review. *Nanoscale* 2017, 9(22), 7342–7372.

- (17) Lee, W.; Park, W.; Park, S.; Sung, S.; Noh, Y. Large-Scale Precise Printing of Ultrathin Sol – Gel Oxide Dielectrics for Directly Patterned Solution-Processed Metal Oxide Transistor Arrays. 2015, 5043–5048.

- (18) Kim, S. H.; Hong, K.; Xie, W.; Lee, K. H.; Zhang, S.; Lodge, T. P.; Frisbie, C. D. Electrolyte-Gated Transistors for Organic and Printed Electronics. **2013**, 1822–1846.

- (19) Kim, B.; Geier, M. L.; Hersam, M. C.; Dodabalapur, A. Inkjet Printed Circuits Based on Ambipolar and P-Type Carbon Nanotube Thin-Film Transistors. *Nat. Publ. Gr.* 2017, 1–8.

- (20) Perelaer, J.; Smith, P. J.; Mager, D.; Soltman, D.; Volkman, S. K.; Subramanian, V.; Korvink, J. G.; Schubert, U. S. Printed Electronics: The Challenges Involved in Printing Devices, Interconnects, and Contacts Based on Inorganic Materials. *J. Mater. Chem.* 2010, 20 (39), 8446-8453.

- (21) Printed, I.; Mobility, H.; Effect, I. F.; Processed, T.; Temperature, R. Inkjet Printed, High Mobility Inorganic-Oxide Field Effect Temperature. **2011**, No. 12, 9628–9638.

- (22) Baby, T. T.; Garlapati, S. K.; Dehm, S.; H??ming, M.; Kruk, R.; Hahn, H.; Dasgupta, S. A General Route toward Complete Room Temperature Processing of Printed and High Performance Oxide Electronics. ACS Nano 2015, 9 (3), 3075–3083.

- (23) Scheideler, W. J.; Kumar, R.; Zeumault, A. R.; Subramanian, V. Low-Temperature-Processed Printed Metal Oxide Transistors Based on Pure Aqueous Inks. *Adv. Funct. Mater.* **2017**, *27* (14), 1606062 (1-11).

- (24) Jeong, S.; Lee, J.-Y.; Lee, S. S.; Oh, S.-W.; Lee, H. H.; Seo, Y.-H.; Ryu, B.-H.; Choi, Y. Chemically Improved High Performance Printed Indium Gallium Zinc Oxide Thin-Film Transistors. *J. Mater. Chem.* 2011, 21 (43), 17066-17070.

- (25) Yu, S. H.; Kim, B. J.; Kang, M. S.; Kim, S. H.; Han, J. H.; Lee, J. Y.; Cho, J. H. In/Ga-Free, Inkjet-Printed Charge Transfer Doping for Solution-Processed ZnO. ACS Appl. Mater. Interfaces 2013, 5 (19), 9765–9769.

- (26) Everaerts, K.; Zeng, L.; Hennek, J. W.; Camacho, D. I.; Jariwala, D.; Bedzyk, M. J.; Hersam, M. C.; Marks, T. J. Printed Indium Gallium Zinc Oxide Transistors. Self-Assembled Nanodielectric Effects on Low-Temperature Combustion Growth and Carrier Mobility. ACS Appl. Mater. Interfaces 2013, 5 (22), 11884–11893.

- (27) Hennek, J. W.; Xia, Y.; Everaerts, K.; Hersam, M. C.; Facchetti, A.; Marks, T. J.

- Reduced Contact Resistance in Inkjet Printed High-Performance Amorphous Indium Gallium Zinc Oxide Transistors. *ACS Appl. Mater. Interfaces* **2012**, *4* (3), 1614–1619.

- (28) Lee, W. H.; Lee, S. J.; Lim, J. A.; Cho, J. H. Printed In-Ga-Zn-O Drop-Based Thin-Film Transistors Sintered Using Intensely Pulsed White Light. *RSC Adv.* **2015**, *5* (96), 78655–78659.

- (29) Nasr, B.; Wang, D.; Kruk, R.; Rösner, H.; Hahn, H.; Dasgupta, S. High-Speed, Low-Voltage, and Environmentally Stable Operation of Electrochemically Gated Zinc Oxide Nanowire Field-Effect Transistors. *Adv. Funct. Mater.* **2013**, *23* (14), 1750–1758.

- (30) Garlapati, S. K.; Baby, T. T.; Dehm, S.; Hammad, M.; Chakravadhanula, V. S. K.; Kruk, R.; Hahn, H.; Dasgupta, S. Ink-Jet Printed CMOS Electronics from Oxide Semiconductors. *Small* 2015, 11 (29), 3591–3596.

- (31) Sunde, T. O. L.; Garskaite, E.; Otter, B.; Fossheim, H. E.; Sæterli, R.; Holmestad, R.; Einarsrud, M.-A.; Grande, T. Transparent and Conducting ITO Thin Films by Spin Coating of an Aqueous Precursor Solution. *J. Mater. Chem.* **2012**, *22* (31), 15740-15749.

- (32) Chen, Z.; Li, W.; Li, R.; Zhang, Y.; Xu, G.; Cheng, H. Fabrication of Highly

Transparent and Conductive Indium–Tin Oxide Thin Films with a High Figure of Merit

via Solution Processing. *Langmuir* **2013**, *29* (45), 13836–13842.

- (33) Secor, E. B.; Smith, J.; Marks, T. J.; Hersam, M. C. High-Performance Inkjet-Printed Indium-Gallium-Zinc-Oxide Transistors Enabled by Embedded, Chemically Stable Graphene Electrodes. *ACS Appl. Mater. Interfaces* **2016**, *8* (27), 17428–17434.

- (34) Nadarajah, A.; Wu, M. Z. B.; Archila, K.; Kast, M. G.; Smith, A. M.; Chiang, T. H.; Keszler, D. A.; Wager, J. F.; Boettcher, S. W. Amorphous In-Ga-Zn Oxide Semiconducting Thin Films with High Mobility from Electrochemically Generated Aqueous Nanocluster Inks. *Chem. Mater.* 2015, 27 (16), 5587–5596.

- (35) Park, W. T.; Son, I.; Park, H. W.; Chung, K. B.; Xu, Y.; Lee, T.; Noh, Y. Y. Facile 22

- Routes To Improve Performance of Solution-Processed Amorphous Metal Oxide Thin Film Transistors by Water Vapor Annealing. *ACS Appl. Mater. Interfaces* **2015**, *7* (24), 13289–13294.

- (36) Jeong, S.; Lee, J.-Y.; Lee, S. S.; Seo, Y.-H.; Kim, S.-Y.; Park, J.-U.; Ryu, B.-H.; Yang, W.; Moon, J.; Choi, Y. Metal Salt-Derived In–Ga–Zn–O Semiconductors Incorporating Formamide as a Novel Co-Solvent for Producing Solution-Processed, Electrohydrodynamic-Jet Printed, High Performance Oxide Transistors. *J. Mater. Chem. C* 2013, *1* (27), 4236-4243.

- Jeon, H.; Song, J.; Na, S.; Moon, M.; Lim, J.; Joo, J.; Jung, D.; Kim, H.; Noh, J.; Lee,

H. J. A Study on the Microstructural and Chemical Evolution of In-Ga-Zn-O Sol-Gel

Films and the Effects on the Electrical Properties. *Thin Solid Films* 2013, 540, 31–35.

- (38) Park, S. K.; Kim, Y. H.; Han, J. I. All Solution-Processed High-Resolution Bottom-Contact Transparent Metal-Oxide Thin Film Transistors. *J. Phys. D. Appl. Phys.* **2009**, 42,125102 (1-6).

- (39) Hwang, S.; Lee, J. H.; Woo, C. H.; Lee, J. Y.; Cho, H. K. Effect of Annealing Temperature on the Electrical Performances of Solution-Processed InGaZnO Thin Film Transistors. *Thin Solid Films* **2011**, *519* (15), 5146–5149.

- (40) Kamiya, T.; Hosono, H. Material Characteristics and Applications of Transparent Amorphous Oxide Semiconductors. *NPG Asia Mater.* **2010**, *2* (1), 15–22.

- (41) Yoon, S.; Kim, S. J.; Tak, Y. J.; Kim, H. J. A Solution-Processed Quaternary Oxide System Obtained at Low-Temperature Using a Vertical Diffusion Technique. *Sci. Rep.* 2017, 7 (January), 1–7.

- (42) Sharma, B. K.; Ahn, J.-H. Instability in an Amorphous In–Ga–Zn–O Field Effect Transistor upon Water Exposure. *J. Phys. D. Appl. Phys.* **2016**, *49*, 055102 (1-8).

- (43) Socratous, J.; Banger, K. K.; Vaynzof, Y.; Sadhanala, A.; Brown, A. D.; Sepe, A.; Steiner, U.; Sirringhaus, H. Electronic Structure of Low-Temperature Solution-

- Processed Amorphous Metal Oxide Semiconductors for Thin-Film Transistor Applications. *Adv. Funct. Mater.* **2015**, *25* (12), 1873–1885.

- (44) Bae, C.; Kim, D.; Moon, S.; Choi, T.; Kim, Y.; Kim, B. S.; Lee, J. S.; Shin, H.; Moon, J. Aging Dynamics of Solution-Processed Amorphous Oxide Semiconductor Field Effect Transistors. ACS Appl. Mater. Interfaces 2010, 2 (3), 626–632.

- (45) Park, S. Y.; Kim, B. J.; Kim, K.; Kang, M. S.; Lim, K. H.; Lee, T. II; Myoung, J. M.; Baik, H. K.; Cho, J. H.; Kim, Y. S. Low-Temperature, Solution-Processed and Alkali Metal Doped Zno for High-Performance Thin-Film Transistors. *Adv. Mater.* 2012, 24 (6), 834–838.

- (46) Hong, K.; Kim, S. H.; Lee, K. H.; Frisbie, C. D. Printed, Sub-2V ZnO Electrolyte Gated Transistors and Inverters on Plastic. *Adv. Mater.* **2013**, *25* (25), 3413–3418.

- (47) Park, S.; Lee, S.; Kim, C. H.; Lee, I.; Lee, W. J.; Kim, S.; Lee, B. G.; Jang, J. H.; Yoon, M. H. Sub-0.5 v Highly Stable Aqueous Salt Gated Metal Oxide Electronics. *Sci. Rep.* **2015**, *5*, 1–9.

**Table 1.** FET parameters such as  $I_{on/off}$ ,  $V_{th}$ , SS, and  $\mu$  at are tabulated for all the devices that are fabricated using different processing schemes and annealing treatments. (AP: All-Printed, S+P: Sputtered electrodes along with printed semiconductor; the associated number indicates the annealing temperature)

| Sample       | $I_{\text{on/off}} (V_{\text{GS}} = 1.0)$ $6 \times 10^4$ | $V_{\mathrm{T}}\left(\mathrm{V}\right)$ | SS  | $\mu$ at $V_{GS}$ = 1.0 (cm <sup>2</sup> /V·s) |

|--------------|-----------------------------------------------------------|-----------------------------------------|-----|------------------------------------------------|

| AP-400       | $6x10^4$                                                  | 0.01                                    | 90  | 0.46                                           |

| AP-450       | 7x10 <sup>5</sup>                                         | -0.12                                   | 100 | 2.4                                            |

| AP-500       | 2x10 <sup>5</sup>                                         | -0.16                                   | 110 | 15.5                                           |

| AP-(500+400) | 2x10 <sup>5</sup>                                         | 0.37                                    | 110 | 5                                              |

| S+P-(400)    | 1x10 <sup>7</sup>                                         | -0.08                                   | 100 | 2.9                                            |

| S+P-(500)    | $1x10^{5}$                                                | -0.46                                   | 184 | 22.7                                           |

## **Figure Captions**

- **Figure 1.** (a) The schematic representations of complete FET fabrication steps in a sequential manner. (b) and (c) XRD patterns of ITO and a-IGZO films, respectively, for different annealing temperatures. (d) and (e) AFM images of printed ITO and a-IGZO layers, respectively, annealed at 400 °C.

- **Figure 2.** Transfer and output characteristics of all-printed FETs with one-step heating at (a) and (b) 400 °C, (c) and (d) 450 °C, (e) and (f) 500 °C, respectively, at  $V_{ds}$  1.0 V. Out-put characteristics are shown at different  $V_{ds}$ .

- **Figure 3.** Transfer and output characteristics of (a) and (b) all-printed FET with two-steps heating at 500 °C for ITO and 400 °C for a-IGZO, (c) and (d) FET with sputtered ITO and printed a-IGZO annealed at 400 °C at  $V_{ds}$  1.0 V, (e) and (f) FET with sputtered ITO and printed a-IGZO annealed at 500 °C at  $V_{ds}$  1.0 V. Out-put characteristics are shown at different  $V_{as}$ .

- **Figure 4.** (a) Schematic representations of an in-plane capacitor with ITO and a-IGZO working electrodes (WE). (b) Charging current loops as a function of a potential sweep at different scan rates in mV per second scale (mVps). (c) Variation of current density (J) as a function of scan rates at different applied potentials. (d) Variation of calculated capacitance values for different applied potentials.

- **Figure 5.** Cross-sectional SEM images of a-IGZO-ITO interface for (a) all-printed one-step annealed, (b) all-printed two-step annealed and (c) sputtered ITO with printed a-IGZO FETs. (d), (e) and (f) show STEM cross-sectional view (top left) of mapped layers (indicated by rectangle) with scale bars 500, 100 and 100 nm and the STEM-EDX elemental maps indicating the diffusion distributions of In, Zn and Sn elements (top right and bottom two panels) for all-printed one-step, two-steps and sputtered ITO with printed a-IGZO, respectively.

- **Figure 6.** Core level spectra of O 1s along with their deconvoluted peaks for (a) ITO, (b) a-IGZO and (c) a-IGZO/ ITO. UPS spectra for (d) ITO, (e) a-IGZO and (f) a-IGZO/ ITO at the juncture where Sn signal starts to appear following the depth profiling. The inset shows the proposed band structure indicating the parameters extracted from UPS.

- **Figure 7.** (a) Schematic representations of n-MOS based logic inverter circuits using three different types of load: a resistor (R-mode), an enhancement type n-MOS (E-mode) and a depletion type n-MOS (D-mode). (b) Input-output characteristics and the corresponding signal gain profiles for inverters constructed using sputtered ITO and printed a-IGZO in R-mode, E-mode and D-mode configurations for  $V_{DD} = 0.5$  V. (c) Input-output characteristics and the corresponding signal gain profiles for all-printed inverter circuit with one-step heating process at 500 °C. (d) Comparison of gain values for sputtered ITO with printed a-IGZO (R-mode, E-mode and D-mode) and all-printed inverters.

**Figure 1.** (a) The schematic representations of complete FET fabrication steps in a sequential manner. (b) and (c) XRD patterns of ITO and a-IGZO films, respectively, for different annealing temperatures. (d) and (e) AFM images of printed ITO and a-IGZO layers, respectively, annealed at 400 °C.

**Figure 2.** Transfer and output characteristics of all-printed FETs with one-step heating at (a) and (b) 400 °C, (c) and (d) 450 °C, (e) and (f) 500 °C, respectively, at  $V_{ds}$  1.0 V. Out-put characteristics are shown at different  $V_{gs}$ .

**Figure 3.** Transfer and output characteristics of (a) and (b) all-printed FET with two-steps heating at 500 °C for ITO and 400 °C for a-IGZO, (c) and (d) FET with sputtered ITO and printed a-IGZO annealed at 400 °C at  $V_{ds}$  1.0 V, (e) and (f) FET with sputtered ITO and printed a-IGZO annealed at 500 °C at  $V_{ds}$  1.0 V. Out-put characteristics are shown at different  $V_{gs}$ .

**Figure 4.** (a) Schematic representations of an in-plane capacitor with ITO and a-IGZO working electrodes (WE). (b) Charging current loops as a function of a potential sweep at different scan rates in mV per second scale (mVps). (c) Variation of current density (J) as a function of scan rates at different applied potentials. (d) Variation of calculated capacitance values for different applied potentials.

**Figure 5.** Cross-sectional SEM images of a-IGZO-ITO interface for (a) all-printed one-step annealed, (b) all-printed two-step annealed and (c) sputtered ITO with printed a-IGZO FETs. (d), (e) and (f) show STEM cross-sectional view (top left) of mapped layers (indicated by rectangle) with scale bars 500, 100 and 100 nm and the STEM-EDX elemental maps indicating the diffusion distributions of In, Zn and Sn elements (top right and bottom two panels) for all-printed one-step, two-steps and sputtered ITO with printed a-IGZO, respectively.

**Figure 6.** Core level spectra of O 1s along with their deconvoluted peaks for (a) ITO, (b) a-IGZO and (c) a-IGZO/ITO. UPS spectra for (d) ITO, (e) a-IGZO and (f) a-IGZO/ITO at the juncture where Sn signal starts to appear following the depth profiling. The inset shows the proposed band structure indicating the parameters extracted from UPS.

**Figure 7.** (a) Schematic representations of n-MOS based logic inverter circuits using three different types of load: a resistor (R-mode), an enhancement type n-MOS (E-mode) and a depletion type n-MOS (D-mode). (b) Input-output characteristics and the corresponding signal gain profiles for inverters constructed using sputtered ITO and printed a-IGZO in R-mode, E-mode and D-mode configurations for  $V_{DD} = 0.5$  V. (c) Input-output characteristics and the corresponding signal gain profiles for all-printed inverter circuit with one-step heating process at 500 °C. (d) Comparison of gain values for sputtered ITO with printed a-IGZO (R-mode, E-mode and D-mode) and all-printed inverters.

## **TOC**